Uibheagan SiC 4 òirleach Fo-stratan SiC leth-inslitheach 6H ìre prìomh, rannsachaidh, agus deuchainn

Sònrachadh Bathar

| Ìre | Ìre Riochdachaidh MPD Neoni (Ìre Z) | Ìre Riochdachaidh Coitcheann (Ìre P) | Ìre meallta (Ìre D) | ||||||||

| Trast-thomhas | 99.5 mm ~ 100.0 mm | ||||||||||

| 4H-SI | 500 μm ± 20 μm | 500 μm ± 25 μm | |||||||||

| Treòrachadh Wafer |

Far an axis: 4.0° a dh’ionnsaigh <1120> ±0.5° airson 4H-N, Air an axis: <0001>±0.5° airson 4H-SI | ||||||||||

| 4H-SI | ≤1cm-2 | ≤5 cm-2 | ≤15 cm-2 | ||||||||

| 4H-SI | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |||||||||

| Prìomh Chòmhnard-stiùiridh | {10-10} ±5.0° | ||||||||||

| Fad Còmhnard Bunasach | 32.5 mm ± 2.0 mm | ||||||||||

| Fad Còmhnard Àrd-sgoile | 18.0 mm±2.0 mm | ||||||||||

| Treòrachadh Còmhnard Àrd-sgoile | Aghaidh silicon suas: 90° CW. bho Prime flat ±5.0° | ||||||||||

| Eisgeachd Iomall | 3 mm | ||||||||||

| LTV/TTV/Bogha/Lùb | ≤3 μm/≤5 μm/≤15 μm/≤30 μm | ≤10 μm/≤15 μm/≤25 μm/≤40 μm | |||||||||

| Garbhachd | Aghaidh C | Pòlainneach | Ra≤1 nm | ||||||||

| Aghaidh Si | CMP | Ra≤0.2 nm | Ra≤0.5 nm | ||||||||

| Sgoltaidhean Oir le Solas Àrd-dian | Chan eil gin ann | Fad cruinnichte ≤ 10 mm, singilte fad≤2 mm | |||||||||

| Pleitean Heics le Solas Àrd-dian | Raon cruinnichte ≤0.05% | Raon cruinnichte ≤0.1% | |||||||||

| Raointean Poileataip le Solas Àrd-dian | Chan eil gin ann | Raon cruinnichte ≤3% | |||||||||

| In-ghabhail Carbon Lèirsinneach | Raon cruinnichte ≤0.05% | Raon cruinnichte ≤3% | |||||||||

| Sgrìoban uachdar silicon le solas àrd-dian | Chan eil gin ann | Trast-thomhas fad cruinnichte ≤1* wafer | |||||||||

| Sliseagan Oir Àrd le Solas Dian | Chan eil gin ceadaichte ≥0.2 mm de leud is doimhneachd | 5 ceadaichte, ≤1 mm gach fear | |||||||||

| Truailleadh Uachdar Silicon le Dian Àrd | Chan eil gin ann | ||||||||||

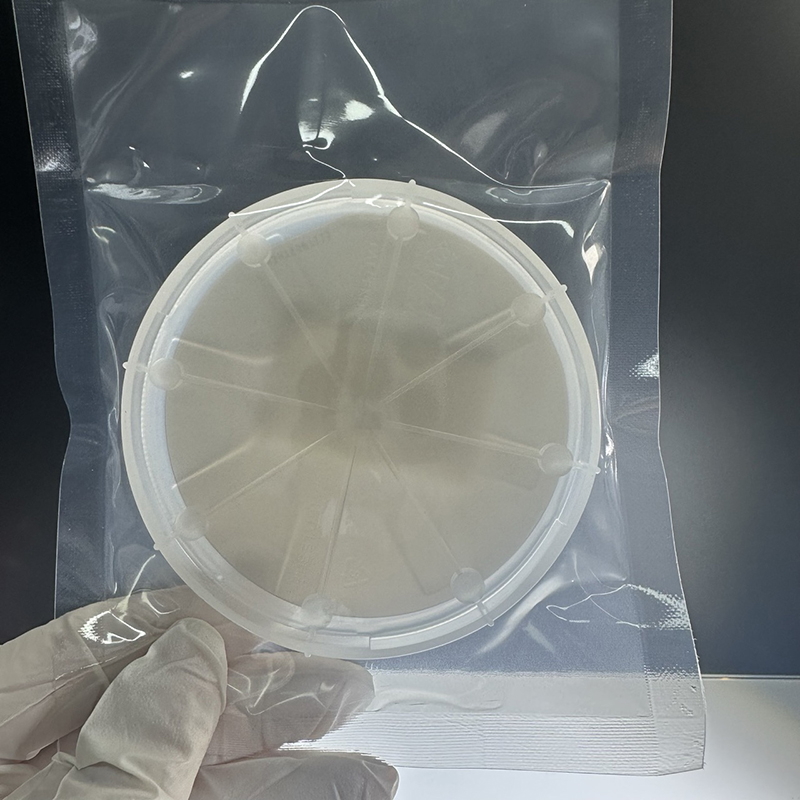

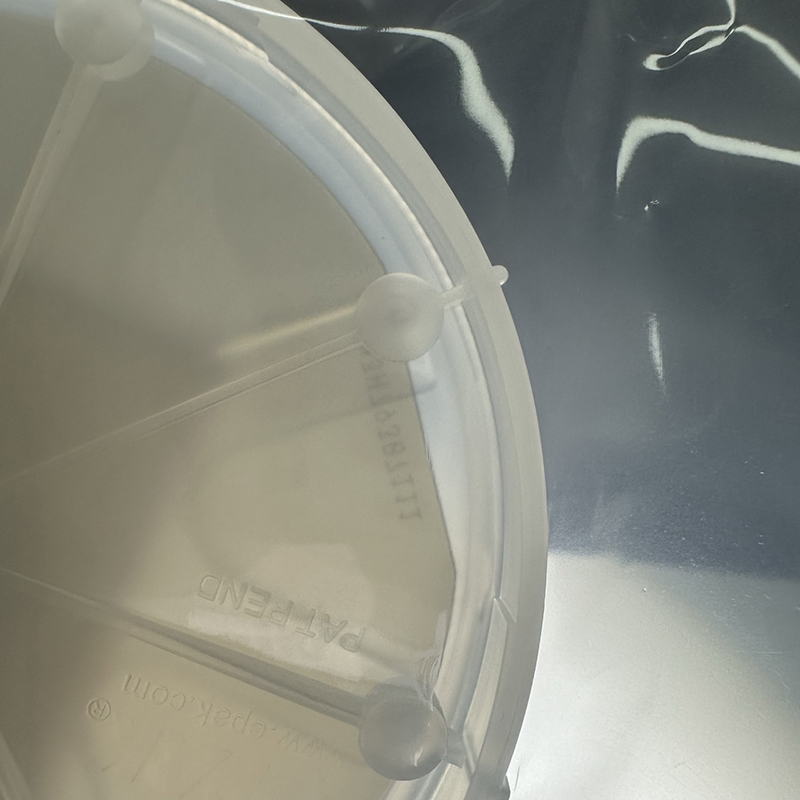

| Pacadh | Caset ioma-wafer no soitheach wafer singilte | ||||||||||

Diagram Mionaideach

Toraidhean co-cheangailte

Sgrìobh do theachdaireachd an seo agus cuir thugainn i